Google Summer of Code 2024

Mentors: Jonathan Balkind and Nils Wistoff

Organization: Free and Open Source Silicon Foundation

Project Page: https://fossi-foundation.org/gsoc/gsoc24-ideas

Synopsis

The growing demand for High-Performance Computing (HPC) requires open-source solutions to meet modern application performance needs. Different open-source architecture frameworks have been developed by the community, such as OpenPiton. However, these frameworks often have performance limitations that hinder their ability to execute compute-intensive tasks.

OpenPiton is an open-source noc designed for many-core processors, which is compatible with different core architectures (RISC-V 32-bit, RISC-V 64-bit, x86, and SPARCv9).In this work, we will focus on implementing the RISC-V cache management operation (CMO) extensions.

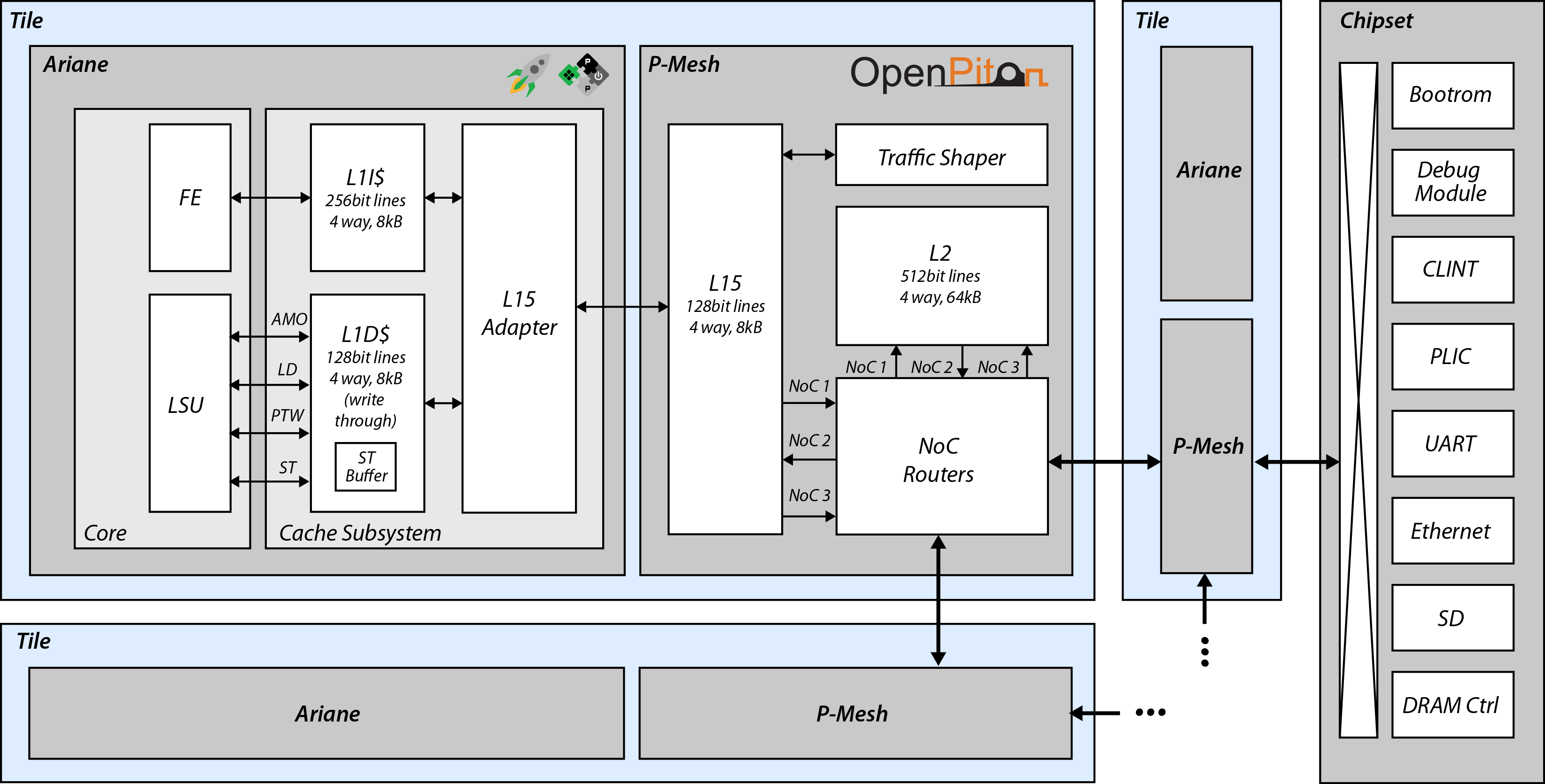

The architecture of OpenPiton comprises one chipset and one or more tiles. The chipset houses modules used to communicate the tiles with the peripherals, such as the UART. The tile is used to build the mesh for many-core designs. In these designs, the tiles are interconnected by three NoC routers to generate the mesh. Each tile comprises the three NoC routers, the Ariane core, and the cache hierarchy, which consists of private L1 data and instruction caches, a private L1.5 cache, and a shared distributed L2 cache.

Project Idea

The project aims to integrate RISC-V Cache Management Operation (CMO) extensions into the OpenPiton processor framework. This integration will improve cache coherency and management, resulting in enhanced performance and efficiency for systems built on the OpenPiton platform. The project will involve understanding the RISC-V CMO specifications, modifying the OpenPiton cache subsystem, and extensive testing to ensure compatibility and performance improvements.

CMO operations:

-

Cache Clean: (cbo.clean) Writes back modified data to the main memory but retains the cache entries. This ensures data coherence between the cache and main memory without discarding the cache contents.

-

Cache Flush:(cbo.flush) Involves writing back all modified (dirty) data from the cache to the main memory and invalidating (clearing) the cache entries.

-

Cache Invalidate: (cbo.inval) Marks cache entries as invalid without writing back any modified data.

Progress Report

-

Update Ariane to the latest version Link

The goal is to update the ariane version to the latest version.Ariane/CVA6 is updated regularly and the new version has changed the interfaces which between the cache subsystem.I had to update the l1.5 adapter to conform to the new interface.

- Support write-through cache

-

CMO core fsm Link

Created a new functional unit which is responsible to handle the different CMO instructions and ensure that correct signals are generated and sent to the cache.

- Forward CMO request to L1.5 cache

-

Forward CMO request from L1.5 to L2 cache

Setup additional encoding/decoding of cmo requests to identify and apply it on the caches.

-

Receive return signal from l1.5 to core cache

Update core cache based on the return signal from the L1.5 cache